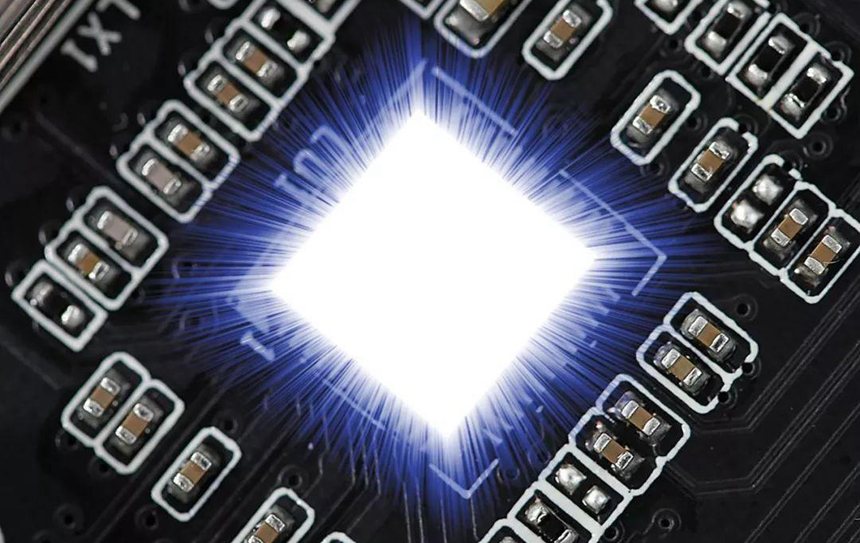

芯片內部是如何互聯的

隨著摩爾定律的放緩,霍爾芯片芯粒(Chiplet)和異構集成 (HI:heterogenous integration) 提供了一種令人信服的方式來繼續改進性能、功耗、面積和成本 (PPAC),但是選擇連接這些設備的最佳方式以使它們以一致且可預測的方式運行是隨著選項數量的不斷增加,這成為一個挑戰。

更多的可能性也帶來更多潛在的連接方式。因此,雖然 AI、5G、高性能計算、移動和可穿戴設備中的下一代應用都受益于不同設備在緊湊封裝中的各種組合,但僅對不斷增加的互連選擇進行分類是一項挑戰。但有利的一面是,該行業不再受一套規則的束縛,定制和優化系統的可能性正在呈爆炸式增長。

Promex工程副總裁 Chip Greely 說:“異構集成的美妙之處在于它現在并不總是適用于電氣。” “你也可以將機電設備放入你的封裝中。對于我們的一些產品領域——例如,醫用相機——我們將機械和電氣功能整合在一個很小的空間內。如果你想擁有一個穩健的制造過程,你就會試圖讓你包括機械接口在內的接口盡可能容忍任何未對準或放置精度的任何變化。”

三星、英特爾、臺積電和許多其他設備制造商正專注于優化各種架構中的芯片到芯片(die-to-die)和芯片到封裝(die-to-package)互連,無論是使用微凸塊、混合鍵合和橋接的垂直構建,還是使用扇出重新分布的水平構建層。決定如何以及在何處形成互連正在成為系統集成的重要組成部分。

封裝選項的數量正在增加,因為許多新設計都是針對特定應用高度定制的。因此,它們的構造和連接方式通常取決于需要處理的數據量和類型、需要處理的位置以及可用功率。例證:特斯拉的 D1 Dojo 芯片是一塊 500 億晶體管芯片,用于在特斯拉數據中心內訓練 AI 模型。特斯拉低壓電子產品副總裁皮特·班農 (Pete Bannon) 在最近的一次演講中表示,這里的重點是海量數據吞吐量,使用具有內置靈活性的高度并行計算。

特斯拉的設備基于臺積電的集成扇出(InFO) 技術,在陣列中包含 25 個 D1 芯粒。Bannon 表示,該設備可以達到 9 petaflops,使用 576 通道的 I/O 環以每秒 36 TB 的速度移動。它還包括 3 個窄 RDL 層和 3 個厚 RDL 層。

與此同時,臺積電的路線圖要求采用可將電阻降低 40% 的新型低電阻互連。臺積電高級副總裁Yuh Jier Mii 表示,該方案不是通過大馬士革(damascene)制造,而是通過帶氣隙而不是電介質的減法金屬反應離子蝕刻(subtractive metal reactive ion etch)制造,可以將電容降低 20% 至 30%,并最終用 2D 互連材料取代銅互連。Mii 在最近的一次演示中表示:“隨著電阻率降低,未來有可能通過增強的互連性能進行擴展。”

異構集成的路線圖正在通過混合鍵合、更多地使用硅橋、二氧化硅和尺寸越來越大的聚合物中介層轉向更多的芯片堆疊。為了滿足不同的最終用途,體系結構和封裝類型不斷增加。

下一篇:談談傳說級芯片設計師Jim Keller 上一篇:臺積電美國廠舉行移機典禮